ABB现场控制单元CRAFTCRAFT012-92599-53

作者: 郭工 来源: 漳州风云电气设备有限公司 查看联系方式 查看评论 2023/7/6 17:56:35

This is the era of 16-bit microprocessors, represented by the Intel 8086. It is relatively mature. [3] (4) The fourth stage (1985-1992). This is the era of 32-bit microprocessors, and the representative product is Intel 80386. Already competent for multi-tasking, multi-user jobs. [3] The 80486 processor released in 1989 realized a 5-stage scalar pipeline, which marked the initial maturity of the CPU and also marked the end of the traditional processor development stage. [1] (5) The fifth stage (1993-2005). This was the era of the Pentium family of microprocessors. [3] In November 1995, Intel released the Pentium processor. This processor adopted the superscalar instruction pipeline structure for the first time, introduced out-of-order execution of instructions and branch prediction technology, and greatly improved the performance of the processor. Therefore, superscalar The instruction pipeline structure has been adopted by subsequent modern processors, such as AMD (Advanced Micro devices) Ryzen, Intel's Core series, etc. [1] (6) The sixth stage (after 2005). Processors are gradually developing towards more cores and higher parallelism. Typical representatives are Intel's Core series processors and AMD's Ryzen series processors. [3] In order to meet the upper-layer work requirements of the operating system, modern processors further introduce functions such as parallelization, multi-core, virtualization, and remote management systems, which continuously promote the development of upper-layer information systems. [1] Working principleEdit The broadcast von Neumann architecture is the foundation of modern computers. Under this architecture, programs and data are stored uniformly, instructions and data need to be accessed from the same storage space, transmitted via the same bus, and cannot be overlapped. According to the von Neumann system, the work of the CPU is divided into the following five stages: instruction fetching stage, instruction decoding stage, instruction execution stage, access to data, and result write-back. [1] Instruction fetch (IF, instruction fetch), that is, the process of fetching an instruction from the main memory to the instruction register. The value in the program counter that indicates the location of the current instruction in main memory. When an instruction is fetched, the Program Counter (PC) is automatically incremented according to the instruction word length. [1] In the instruction decoding stage (ID, instruction decode), after the instruction is fetched, the instruction decoder splits and interprets the retrieved instruction according to the predetermined instruction format, and identifies and distinguishes different instruction categories and various acquisitions. method of the operand. Modern CISC processors will split to increase parallelism and efficiency. [1] Executing the command stage (EX, execute), which specifically realizes the function of the command. The different parts of the CPU are wired together to perform the required operations. In the stage of access and access (MEM, memory), the main memory is accessed and the operand is read according to the instruction. The CPU obtains the address of the operand in the main memory, and reads the operand from the main memory for calculation. Some instructions do not need to access main memory, this stage can be skipped. [1] The result write back stage (WB, write back), as the last stage, the result write back stage 'writes back' the operation result data of the instruction execution stage to a certain storage form. The result data will generally be written into the internal registers of the CPU so that they can be quickly accessed by subsequent instructions; many instructions will also change the status of the flag bits in the program status word register. These flag bits mark different operation results and can be accessed by Used to affect the actions of the program. [1] After the instruction is executed and the result data is written back, if there is no unexpected event (such as result overflow, etc.), the computer will obtain the address of the next instruction from the program counter and start a new cycle. The next instruction cycle will be Fetch the next instruction sequentially. [1] Many complex CPUs can extract multiple instructions at0ne time, decode them, and execute them at the same time. Its function is mainly to interpret computer instructions and process data in computer software. The CPU is the core component in a computer responsible for reading instructions, decoding them, and executing them. The central processing unit mainly includes two parts, namely the controller and the arithmetic unit, which also include the cache memory and the data and control bus that realize the connection between them. The three core components of an electronic computer are the CPU, internal memory, and input/output devices. The function of the central processing unit is mainly to process instructions, perform operations, control time, and process data. [2] In the computer architecture, the CPU is the core hardware unit that controls and allocates all the hardware resources of the computer (such as memory, input and output units) and performs general-purpose operations. The CPU is the computing and control core of a computer.

版权提示】一步电子网倡导尊重与保护知识产权。未经许可,任何人不得复制、转载、或以其他方式使用本网站的内容。如发现本站文章存在版权问题,烦请提供版权疑问、身份证明、版权证明、联系方式等发邮件至web@kuyibu.com,我们将及时沟通与处理。

猜你喜欢

AI与PLC工程师,谁才是工控行业的主角?

2024/6/4 13:55:17

三棱为扬力集团构建电气焊智能管理系统

2024/6/4 13:55:13

英飞凌:以低碳化、数字化为引擎,驱动本土业务持续增长

2024/6/4 11:55:15

松下伺服电机MSM022P1E维修周期短

2024/6/4 8:52:34

宝盟编码器报警维修信息了解

2024/6/4 8:52:05

APD伺服马达维修详情必读

2024/6/4 8:51:09

华中数控伺服电机报警维修 电机失速

2024/6/4 8:44:04

YASKAWA伺服电机SGM7J-08AFC6S维修攻略全

2024/6/4 8:42:36

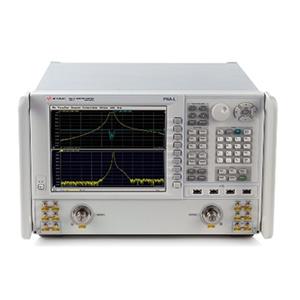

原装N5222A网络分析仪租赁

2024/6/3 18:21:32

租赁二手N5221B网络分析仪,13.5GHz

2024/6/3 18:15:02

租赁Agilent83732B/HP83732B高频信号发生器

2024/6/3 18:12:05

原装FSV13频谱分析仪租赁

2024/6/3 18:10:07

发表评论 点击 登录 微信,亮头像秀观点,已发布 0 条